프리랜서와 1인 기업에 AI 에이전트 확산이 미칠 영향

AI 에이전트 확산은 프리랜서와 1인 기업의 생산성을 끌어올리는 동시에 경쟁 기준을 높이고 있다. 반복 업무 자동화로 업무량은 줄지만 차별화는 전문성과 신뢰로 이동하는 흐름이 나타난다.

5분 소요

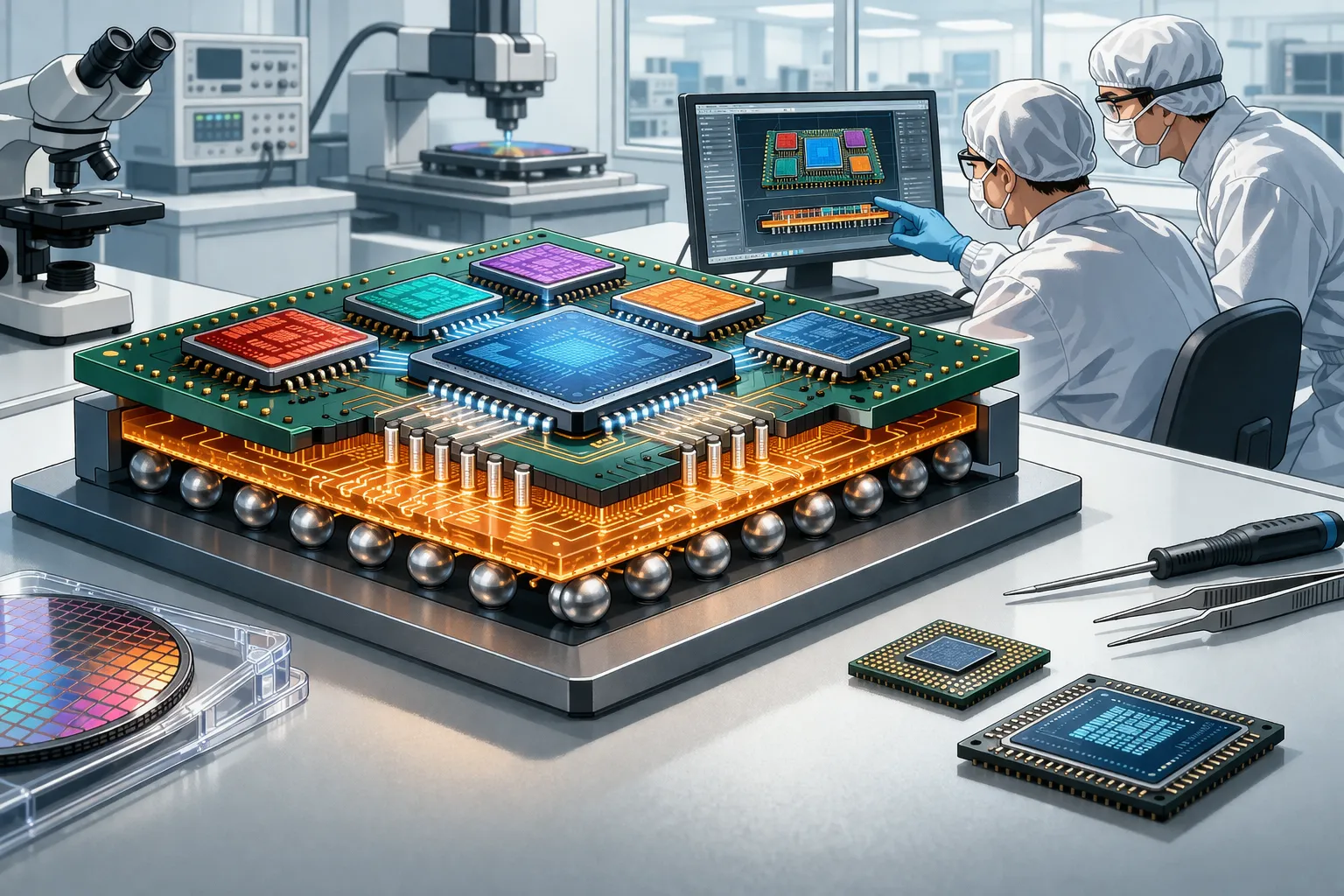

반도체 설계 방식이 변하고 있다. 하나의 거대한 칩에 모든 기능을 담는 방식은 점점 부담이 커지고 있다. 칩 면적이 커질수록 제조 과정에서 불량이 발생할 가능성이 높아지고, 수율 저하는 곧 비용 상승으로 이어진다. 설계 복잡도도 함께 올라간다. 이 문제를 해결하기 위한 대안으로 칩렛 구조가 빠르게 자리 잡고 있다.

칩렛 구조는 기능별로 나뉜 여러 개의 작은 다이를 하나의 패키지 안에서 연결해 하나의 시스템처럼 동작하게 만드는 방식이다. 중앙처리장치(CPU), 그래픽처리장치(GPU), 입출력 회로, 메모리 제어기 등을 각각 분리해 제작한 뒤 하나로 묶는다. 기존에는 하나의 실리콘 덩어리에 이 모든 기능을 담았지만, 이제는 모듈처럼 나눠 조합하는 흐름으로 이동하고 있다.

이 변화의 배경에는 비용 문제가 있다. 공정 미세화가 진행될수록 웨이퍼 가격은 상승하고 설계 난이도도 높아진다. 큰 칩 하나를 만드는 대신 작은 칩 여러 개로 나누면 각각의 다이에서 발생하는 불량 영향을 줄일 수 있다. 결과적으로 전체 생산 수율이 개선된다. 동일한 설계를 반복 활용할 수 있어 재사용성도 높아진다. 이는 개발 기간과 비용을 동시에 줄이는 요소로 작용한다.

공정 선택의 유연성도 칩렛 구조의 장점으로 꼽힌다. 모든 기능을 동일한 공정에서 만들 필요가 없다. 연산 성능이 중요한 영역은 최신 공정을 적용하고, 상대적으로 민감도가 낮은 입출력 회로나 주변 기능은 안정된 공정을 사용할 수 있다. 이 방식은 비용과 성능 사이에서 균형을 맞추는 데 유리하다. 하나의 칩 안에서 타협해야 했던 설계 제약이 줄어든 셈이다.

확장성 역시 중요한 변화다. 칩렛은 블록처럼 추가할 수 있다. 더 많은 연산 성능이 필요하면 동일한 칩렛을 추가로 배치하는 방식으로 대응할 수 있다. 서버나 인공지능 연산 장치처럼 성능 요구가 빠르게 증가하는 분야에서 이 구조는 특히 효과적이다. 새로운 대형 칩을 처음부터 설계하지 않아도 제품군을 다양하게 구성할 수 있다. 시장 대응 속도도 빨라진다.

하지만 칩렛 구조는 단순한 분할이 아니다. 여러 칩을 하나의 제품으로 만들기 위해서는 고성능 연결 기술이 필요하다. 패키지 내부에서 데이터를 빠르게 주고받아야 하기 때문이다. 이를 위해 2.5D 패키징, 3D 적층 기술이 활용된다. 실리콘 인터포저를 사용해 칩 간 거리를 줄이고 대역폭을 확보하는 방식이 대표적이다. 메모리와 연산 칩을 가까이 배치해 지연 시간을 줄이는 설계도 함께 적용된다.

연결 기술과 함께 표준 경쟁도 시작됐다. 서로 다른 회사가 만든 칩렛을 하나의 패키지에서 사용할 수 있어야 생태계가 확대된다. 이를 위해 UCIe(Universal Chiplet Interconnect Express)와 같은 개방형 인터커넥트 규격이 등장했다. 이 규격은 칩렛 간 데이터 전송 방식과 물리적 연결 구조를 정의한다. 공통 규칙이 마련되면 다양한 업체가 참여할 수 있고, 조합의 자유도도 높아진다.

그러나 해결해야 할 과제도 분명하다. 여러 다이를 하나로 묶으면 전력 분배가 복잡해진다. 발열 관리도 어려워진다. 칩 간 신호 지연과 간섭 문제도 고려해야 한다. 설계 단계에서 검증 범위가 넓어지고 테스트 과정도 까다로워진다. 제품 출시 전 확인해야 할 요소가 늘어난다는 의미다. 운영 중 문제를 추적하고 수정하는 과정도 복잡해진다.

칩렛 구조는 설계 방식의 변화에 그치지 않는다. 패키징 기술, 인터커넥트 규격, 검증 체계가 함께 움직여야 한다. 반도체 산업 전반이 이 구조에 맞춰 재편되는 흐름이다. 성능 요구가 계속 증가하는 상황에서 단일 칩 방식만으로는 대응이 어려워졌다. 이 흐름 속에서 칩렛은 비용과 성능, 확장성 사이의 균형을 찾기 위한 선택으로 자리 잡고 있다.

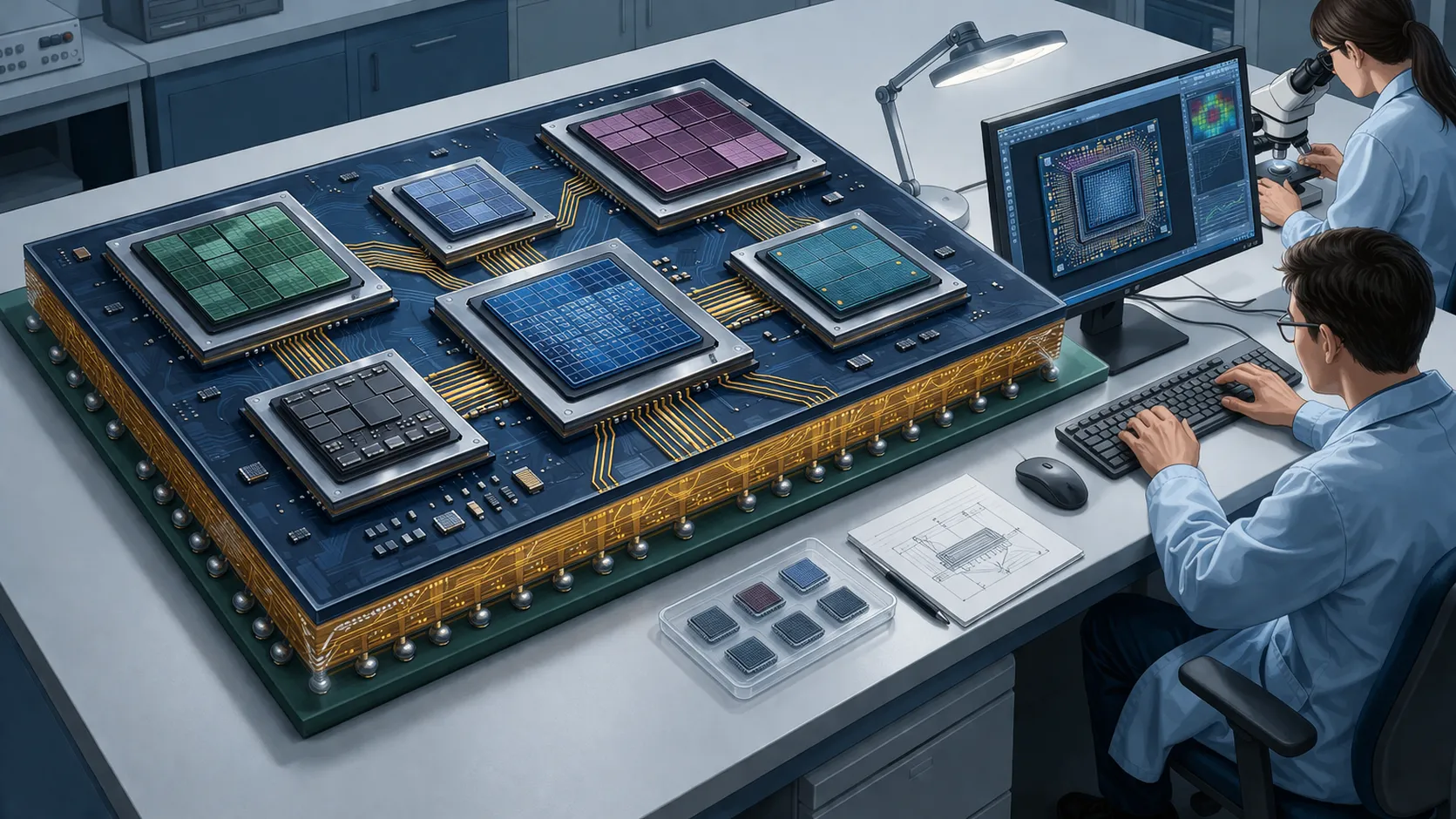

반도체 산업은 칩 크기가 커질수록 발생하는 구조적 문제에 직면해 왔다. 하나의 칩에 더 많은 기능을 넣기 위해 면적을 키우는 방식은 설계 난이도를 높인다. 공정이 미세해질수록 제조 과정에서 작은 결함도 전체 칩 불량으로 이어질 수 있다. 이로 인해 생산 수율이 낮아지고 비용 부담이 커진다. 이러한 상황은 고성능 연산이 요구되는 분야에서 더욱 두드러진다.

설계 복잡도 증가도 중요한 문제로 지적된다. 단일 칩에 CPU, GPU, 메모리 제어, 입출력 기능을 모두 포함하면 설계 검증 과정이 길어진다. 오류를 찾고 수정하는 데 많은 시간이 필요하다. 개발 일정이 지연되면 시장 대응 속도도 떨어진다. 반도체 기업은 설계 효율을 높일 수 있는 구조를 요구받게 됐다.

이 문제를 해결하기 위해 등장한 방식이 칩렛 구조다. 기능을 나눈 작은 칩을 각각 설계한 뒤 하나의 패키지에서 연결한다. 작은 단위로 나누면 각각의 칩에서 발생하는 불량 영향이 제한된다. 동일한 칩을 여러 제품에 활용할 수 있어 재사용성도 높아진다. 설계와 생산 과정에서 부담을 분산할 수 있는 구조다.

공정 선택의 제약도 칩렛 구조 도입을 촉진한 요인이다. 모든 기능을 하나의 공정에서 처리하면 비용이 상승한다. 칩렛 구조에서는 연산 기능과 입출력 기능을 다른 공정으로 제작할 수 있다. 성능이 중요한 부분에는 최신 공정을 적용하고, 상대적으로 요구 조건이 낮은 부분에는 안정된 공정을 사용할 수 있다. 이 방식은 비용과 성능 간 균형을 맞추는 데 유리하다.

성능 확장 요구 역시 구조 변화를 이끌었다. 인공지능 연산, 서버 처리 환경에서는 코어 수와 데이터 처리량이 빠르게 증가한다. 단일 칩으로 대응하면 설계 부담이 커진다. 칩렛은 필요한 만큼 추가할 수 있는 구조를 제공한다. 동일한 설계를 반복 사용해 다양한 성능 구성을 만들 수 있다. 이는 제품 개발 속도를 높이고 시장 요구에 유연하게 대응할 수 있게 만든다.

최지환

최지환기술의 본질과 그 파급력을 깊이 있게 탐구하며, IT 산업 전반에 걸친 변화의 흐름을 날카롭게 짚어내는 데 집중하고 있습니다. 인공지능, 클라우드, 반도체, 사이버보안 등 빠르게 진화하는 분야에서 핵심 이슈를 선별하고, 일반 독자도 쉽게 이해할 수 있도록 맥락을 갖춘 보도를 지향합니다. 기술 자체보다는 그것이 산업과 사회에 어떻게 작용하는지를 관찰하고, 기업 전략, 기술 규제, 사용자 경험 등 다양한 관점에서 접근합니다. 각종 기술 행사와 컨퍼런스를 직접 취재하며, 깊이 있는 분석과 균형 잡힌 시각으로 독자의 신뢰를 쌓아가고 있습니다.

AI 에이전트 확산은 프리랜서와 1인 기업의 생산성을 끌어올리는 동시에 경쟁 기준을 높이고 있다. 반복 업무 자동화로 업무량은 줄지만 차별화는 전문성과 신뢰로 이동하는 흐름이 나타난다.

5분 소요

AI가 평균적 콘텐츠를 빠르게 생산하면서 정보의 양보다 전달자의 신뢰가 중요해지고 있다. 개인 브랜드는 홍보 수단이 아니라 신뢰를 구분하는 기준으로 자리 잡고 있다.

6분 소요

AI 에이전트가 빠르게 보급되지만 성과는 균등하지 않다. 질문 설계, 맥락 제공, 결과 검증, 업무 연결 능력에 따라 생산성 격차가 확대될 가능성이 크다. 기업은 도입보다 리터러시와 워크플로 재설계에 주목하고 있다.

6분 소요

AI 에이전트는 개인 업무 도구를 넘어 조직의 정보 흐름과 의사결정 방식을 바꾸고 있다. 보고 체계 단순화, 회의 축소, 문서 역할 변화가 동시에 나타나며 조직문화 전반에 영향을 준다.

6분 소요

교육 현장에서 AI 에이전트 사용을 둘러싼 논쟁이 이어지고 있다. 전면 금지보다 조건부 허용과 설계된 활용이 더 현실적이라는 인식이 확산된다. 과제 구조와 평가 방식 변화가 함께 요구된다.

6분 소요

AI 에이전트 사고 책임은 AI 자체가 아니라 인간 조직에 귀속된다. 개발사 설계 책임, 도입 기업 운영 책임, 승인자의 행위 책임이 동시에 작동하며 자율성이 커질수록 책임 기준도 더 정밀해진다.

6분 소요

AI 에이전트는 창의성을 높일 수도 낮출 수도 있다. 연구들은 품질 향상과 함께 아이디어 다양성 감소를 함께 보여 준다. 핵심은 어떤 단계에서 AI를 쓰고 인간이 어디까지 개입하느냐에 달려 있다.

5분 소요

중소기업은 인력과 자원 한계로 작은 비효율도 큰 부담으로 이어진다. AI 에이전트는 반복 업무를 줄이고 생산성을 높이는 수단으로 작용한다. 도입이 늦어질수록 대기업과의 격차는 더 벌어질 수 있다.

6분 소요